�������Ƕ���ͨѶ��·�Լ�����������������վ�������Ч��ͨѶϵͳٲȻ�ѳ�Ϊ�ֽ���Ϊ��Ҫ�ķ�չ���⡣����ͨѶ�������ʴ��������ʱ��������jitter������ϵͳ����������ص�Ӱ�죬���Բ����κ���ز�Ʒ�Ա���ͨ����������֤��ſɽ����������м��ڴˣ��ڱ����н����һ�ڽ��������Լܹ���Ҳ���Dz��ö����Ŵ�ԭ�������������ɣ�Pulse Remove��PR��֮������ʵ�ֳ���ȷ������Ч�ʵ��ڽ��������Ե�·���Լ����ⲿ����֮���������������������Գɱ���

ǰ��

ʱ����timing jitter��Ϊϵͳ������ձ���ڵ����⡣������Ϊ����ϵͳʹ�����������ߣ����Խ����ϵ͵�Ѷ�Ŵ����ٶȼ�����Ƹ�����Ҳ��˶����������������ʱ����ռ�ı����dz�С�����Ż����·�������죬�����ռ�ʹ�õ��Բ�����ͨѶƵ�������ڸ���ͨѶЭ���϶��������������ٶȡ�����ͬ������ʱ������Ѷ�ż�ռ���൱��İٷֱȡ������ʱ����ص�ϵͳ������Զ�������һ���Ĺ淶��

Ŀǰ��������ȡ�ķ�ʽ�Խ��������ⲿ�������ã�����ϵͳ�����������Ӻ��������ϻ����������������⣺���Գɱ���cost�������ȷ�ȣ�accuracy�����Ӳ��Գɱ��۵���������Ҫ����GHz����Ѷ�ţ�ʾ����Ϊ�õ�ȷ������ֵ��ȡ���ʱ���dz����٣�������ʮGS/s�������Ӳ��ʵ�ֱ�÷dz����ѣ����Ի�̨�ɱ�Ҳ�ʹ�����������⣬�����ⲿ�������Ծ�Ƭ�ڲ�Ѷ�ţ�Ҳ���������ɿ��ȵ����⡣������Ի������ڴ���Ѷ�ŵĸ��š�I/O����Ƶ��֮���ơ���Ƭ�ڲ������������output buffer������Ѷ…�ȵȣ���Щ�Ի����������ֵȷ���½���

Ϊ�����ز������⣬Ŀǰ������Ŀ�ķ������Ǽ���ɲ�������ƣ�Design for Testability��DfT�����ɲ�������ƵĹ���������������м�������Ŀ��������ǽ���һЩ���⸨�����㷽ʽ�����Ͷ��Զ������豸���ܵ�Ҫ���������������������֮�ɱ���ʱ�䡣Ȼ���˲��Է�ʽ��ɼ��ٲ��Գɱ���ʱ�䣬����г���ڸ��������ȷ�ԡ�������Ϊ�����·����ע����Ѷ�ڴ����·�У���Ҳ��ȷ���˵�·����Ƿ����ƣ��������ö�������㷽ʽ������ȷ��������ֵ���Ǵ�����趨��������������̲���ʱ��Ҳ��ͽ������

���Ľ����һ���ڽ��ھ�Ƭ������ʱ��������֮�����뷨��ܹ�������õ�ߢȡ��single-shot�����ⷽʽ����ʱ��Ŵ�ļ��ɽ�Ѷ�Ŷ������ȱ������ӣ�������ʱ����λת����·��Time-to-Digital Converter��TDC�����Ƴ��ϵ����ơ������������Խ����ȣ�resolution�����������ʹ����������֮��·������ʹ�üܹ����м������Զȡ�����봫ͳ�ڽ����������·��[1]~[5]������߱���Ƶ�����Լ��Ͷ���������֮���ԣ����н�С�ij�������ʣ�area overhead����

Background

��չ�����ڽ�ʱ���������Լ����м��ֽ�Ϊ�ձ�IJ��Լܹ�����Щ��Ӧ����ҵ���Ʒ�����У��������Щ��ͳ�ܹ�����һ�����ܡ�

Delay Chain [1]

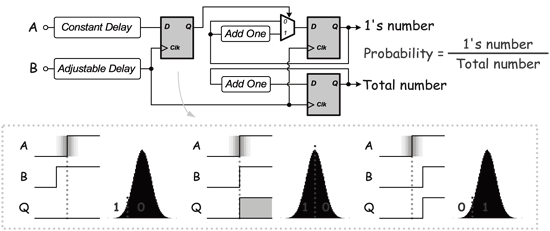

��ͼһ��ʹ��delay chain֮�������ⷨ��

�˲��Լܹ�ΪLogic Vision��1999������������ÿɵ����ӳ��ߣ�Adjustable Delay Line��ADL���������������������ͳ��ԭ�������Զ��������������ͺñ���һ����λ��������������ӳ���ʹ��B��ǰA����ʱ0���ֵĻ��ʽ�ռ��������֮��B�����A����1���ֵĻ��ʽ�ռ�������༴���ɵ�����ͬ�ӳ������õ���ͬ���ʷֲ����ٴ������ۻ��ֲ����������㣨Cumulative Distribution Function��CDF�������������������

�ŵ㣺

��ܹ���������ʵ�֡�

ȱ�㣺

���ӳ�����Ƶ�ʵ����ƣ��˽�Ӱ�������Χ��

��������ӳ�ʱ�����õ�1��0�ֲ�������֪����������˽����߳��IJ���ʱ�䡣

Two Ring Oscillators [2]

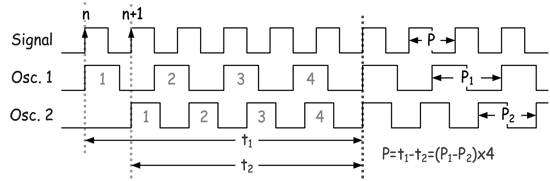

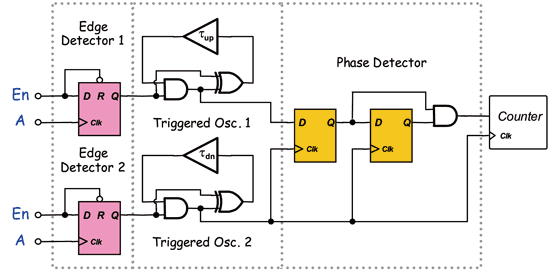

��ͼ�� ʹ��two ring oscillators֮�������ⷨ��

�˲��Լܹ���ΪCredence��1999�����������ʹ��������֪����ͬ����Ƶ�ʵ��ڽ����������ô���ʱ��Ѷ�ŵĵ�n�����n+1�����ڷֱ�ȥ��������ʹ�俪ʼ�������߲�ͬ����ʱ��֮��λ�ǺϺ���������λ�Ǻ���������������������ڼ��ɷ���ʱ����������

�ŵ㣺

����ô����ķ�ʽ��Ѷ�Ų�����Ϊ����delay chain��duty cycle���ܵ�Ӱ�죬�����ǰ����������нϹ�����ⷶΧ��

ȱ�㣺

�����Ǿ�������ڱȽϺ����ã���˲���ʱ�佫�����Ŀ�����

��ʹ����������֮��λ�Ƚ����õ�������������Ƶ��Ư�ƽ���ɲ�����

��������ͳ�Ƶ�·�������ɱ��ϸߡ�

Vernier Delay Line [3]

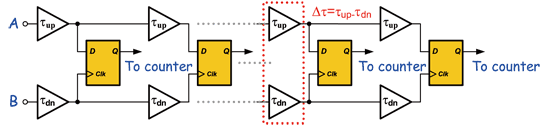

��ͼ�� ʹ��vernier delay line֮�������ⷨ��

�α��ӳ��ߣ�Vernier Delay Line��VDL��ΪĿǰ������õĶ������Լ�������Piotr Dudek��2000 JSSC������������ԭ���ǽ��ο������ʱ���ֱ�����������ͬ�ӳ�����τup��τdn����delay chain�У��������ж��������ڣ����ӳٵ�Ԫ�������ƽ�������n�����ں���Ѷ��ͬ��λ������λ��ǰ������״̬�ı䣬�������������Ϊnx��τ�����С�τ=τup-τdn�����Խ��ɴ˲��Լ������ɲ��Ե��ڴ���բ��sub-gate���Ķ�������

�ŵ㣺

��ʹ���ӳ�ʱ���Ĺ�����ʵ�֣��ɾ��нϼѵIJ��Խ����ȣ�=��τ����

ȱ�㣺

���Ƴ̱�������ȷ��ÿ���ӳٵ�Ԫ֮�ӳ�ʱ������ȣ��˽�Ӱ�����ȷ�ȡ�

ADC Sampling [4]

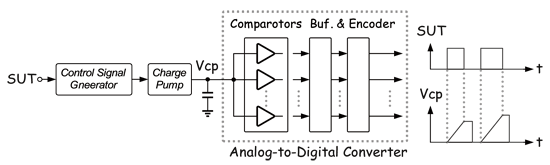

��ͼ�� ʹ��ADC sampling֮�������ⷨ��

��Ϊʱ��ı仯������һ����Լܹ����Ǵ�ʱ���������֪����Henery C. Lin��2003 ITC�У�����ʱ��ת��ѹ�ķ�ʽ��ʵ�ֶ��������ԡ������������һ���ɰ��֣�������Ѷ��Ϊ�ߵ�λʱ������Ը��س�磻���ڵ͵�λʱ�ͽ���ѹλ���ù��㡣���Դ���Ѷ����������Խ�����õĵ�ѹֵҲ��Խ�ߣ���֮�������Ƚ�С��ѹҲ����֮���͡�����������ADC����ѹλת������λ������ö�������

�ŵ㣺

���ڵ���ʱ�������о��нϸ�֮�����ȡ�

�����real time�����������ʱ�佫�����̡�

ȱ�㣺

����Խ�����������ٶȽ�ȡ����ADC֮��ơ�

���ڵ�ѹ����ʱ���ܴ�ֱ����Ӱ��������½����ȴ���½���

Component-Invariant VDL [5]

��ͼ�� ʹ��component-invariant VDL֮�������ⷨ��

���һ�ֲ��Լܹ�ΪG. W. Roberts��2001 ITC����������ֲ��÷DZ�����Ԫ��֮�α��ӳ��ߺ�[03]��������ʵ�dz����ơ���������һ�����ӳٵ�ԪȻ����Ѷ�Ż��������һ������ȷ����������Ƚ�Ϊ��t������n�������ں������ӳ�����λ�ı������ͬʱ�������[03]�������������������

�ŵ㣺

��ÿ���ӳٽ�Ϊ��t����������ȷ�ȡ�

��ʹ�������ӳ���֮�������ⶶ��������˿ɾ��нϸ߽����ȡ�

ȱ�㣺

���[02]�ܹ�һ����ϳ��IJ���ʱ�䡣

����������������ֲ��Է��ɿ�������Ŀǰ�IJ��Լ������ԣ������������signal amplitude sampling�Լ�time domain analysis���ַ�����ʵ�֡�����ǰ����˵�������Ƴ̽���������ѹ���ͣ�������������ADC��Ƶ�ƿ�������Խ������ѽ����˲��ô�������ʵ�ֶ��������ԡ���������ܹ�ʵ����ʽ������ͬ������������ʱ����λת����Time-to-Digital Converted���Ĺ�����ʵ�֡�Ȼ����Щ�ܹ����й�ͨ�����⣬���Dz������ʲ����Լ������Ȳ��ߡ���Ŀǰ������PC�ܱ߲�Ʒ��˵���ձ��ٶȽ����ڼ���MHz�ȼ�����CPU���Ǵ����������Ͽ���GHz�ȼ������ⶶ�����ڸ���ϵͳ�����ֵԼ��������ʮps������������ϵͳû�кõĽ����ȺͿ���Χ����֮�����������б����Ѷ��֮�û�����˱��Ľ����һ���µĶ��������뷨��ܹ�����Ը�����Ͷ���ʱ��������ȷ��precision�����ȷ��accuracy��֮�������ԡ�

Proposed Technique

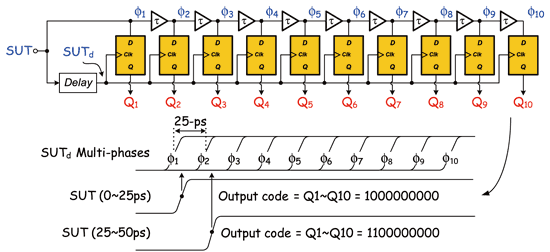

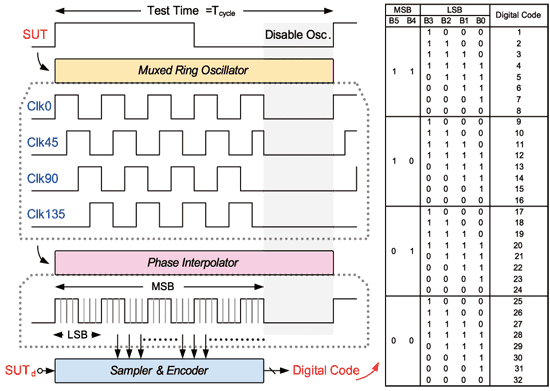

��ͼ�� ��ͳʱ��-��λת������֮ʾ��ͼ��

�ڽ������������֮���Է���ǰ������̽�ִ�ͳ���Ե����⡣ͼ��Ϊ��ͳʱ��-��λת���Ĺ��̡���һʱ����SUT����������ʱ�����Ե���뿪ԭ�������λ�ã���ʱ�ձ�������ὫSUT�ӳ�һ������ʱ�䣨SUTd����ȥ����En��En+1��Ե֮�����̶ȡ������Է������ǽ�SUT����delay chain�е�����ȡ�������ϣ���SUTd����Ϊȡ��ʱ������SUTd�Ծ�����ͬ�ӳ���֮SUT��ȡ����������¶��루thermal code������λ���ϣ���������ϼ�������ͬʱ����������

������˵����Ŀǰdelay chainΪ10��25-ps�ӳ���֮�ӳٵ�Ԫ����ɣ���ʱʱ�����ڶ����ڶ�����Ϊ10-ps����ȡ�����õ�1000000000����λ�룻������������Ϊ30-ps��������1100000000����˶�����Խ����λ���е�1Ҳ�ͻ�Խ�ࡣ����Ŀǰ�ļ��������Դ����뷨��ʵ�ֶ��������ԣ�����֮ͬ�����ǻ����������·���ɽ��ӳٵ�Ԫ���ӳ�����С����߲��Խ����ȣ����α��ӳ��ߡ��ڲ�…�ȡ�

��������˵�����ɵ�֪����Ϊ�����Ⱥ��ӳٵ�Ԫ֮�ӳ����ɷ��ȣ������������ӳ�����Ƶ÷dz�С����Եؾͻ�����������������ǰ����˵�������ϵ�������Ϊ0.1-ps��24.9-psʱ���õ�����λ���Ϊ1000000000�������������ӽ�һ���ӳ�ʱ�䡣����˵���ڸ��ٵͶ�����Ӧ���У��˲������������˵������ʹ���ߡ����������õ�·�ϵļ��������ӳ�ʱ�������������仹�ǻ����Ƴ������м���ֵ���ڣ���ͨ����ķѽϴ��Ӳ��������������Ƿ���˼��������ʱ��-��λת����Ϊ�����㣬������һ��·�����ȷŴ����ڶ�����֮�����������һ�����ɼ��ٲ��Ե�·��Ƶ����ѶȲ��������Խ����ȡ�

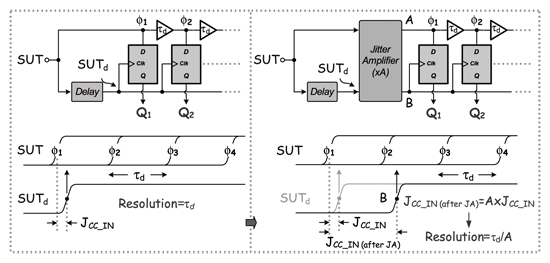

��ͼ�� �������Ŵ�֮����ͼ��

��ͼ��Ϊ�������ӳٵ�Ԫ���ӳ�ʱ��Ϊτd������������κθ�����·������ѽ����ȼ�Ϊτd������������Ĺ۵�����������ʱ�Ƚ����붶�����Ŵ�A������delay chain�У�Ч������ͬ���ӳ�ʱ�����������Ӳ��Խ����ȣ�Ҳ������ʱ�����ܹ���ѽ����ȱ�ɵ�Ч��”τd/A”��

������˵����0.13-um�Ƴ�����Сբ�ӳ�ʱ��Ϊ25-ps�����Բ��ô�ͳ������Լֻ������Ķ�����Ϊ25-ps���������ڶ�����ת������λ��ǰ�Ƚ���Ŵ�25��������ѽ����ȼ�������1-ps��25-ps/25��������֮�⣬���Ŷ����Ŵ���A����τd�����ӳٵ�Ԫ���ӳ�ʱ��С��1-ps��τd/A<1�������Դ�ʱ�������sub-pico-second�ȼ�֮�����������ԡ�

��˱��������Ը�����ǽ��ɷŴ�����ʱ�����ڶ�����֮����������������ʱ��-��λת����·�IJ��㣬�Ҹ���һ���������Խ����ȣ����ô˲���ϵͳ�����ڸ��ٵͶ�������ϵͳ���м���ȷ�ȡ�ͼ�˼�Ϊ���������֮�����Ŵ�ԭ����ʵ�ֵ��ڽ�ʱ��������֮���Լܹ���

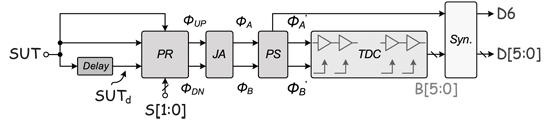

��ͼ�� �����֮�ڽ�ʱ�����������Լܹ���

��������������ɵ�·��Pulse Remover��PR���������Ŵ��·��Jitter Amplifier��JA������λѡ���·��Phase Selector��PS����ʱ��-��λת����·��Time-to-Digital Converter��TDC����ͬ����·��synchronizer��������PR��JA֮��������������붶���������ԷŴ�TDC�Ĺ�����ɰѶ�����������λ�룻����ͬ����·�Ὣ���е������λ����ͬ���������������Ӳ��֮���������ڴ����ֻ���ij����ڶ����ڼ�֮�������������ж�Ŀǰ��Ե��Ĺ�ϵ������λ����

�����TDCǰ����һPS[6]���������ж�Ŀǰ��λ��ϵ������ΦA��ΦB����TDCǰ˭�������϶�˭����ȡ��ʱ������ΦA��ǰΦB����D6ΪHi��ΦA’=ΦA��Φ’=ΦB��������������֮��ΦB��ǰΦA����D6ΪLow��ΦA’=ΦB��ΦB’=ΦA�����ڷ��������ô�λԪ֮������ɸ���ȷ�ж϶���֮��̬�����������Ǿ���Ը���Ҫ��·����һ���Ľ��ܡ�

�����Ŵ��·��Ƽܹ� [7] [8]

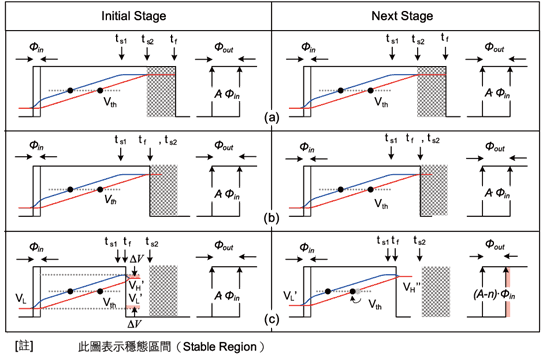

��ͼ�� �����Ŵ��·֮�ܹ�ͼ��ʱ��ͼ��

���ڶ����ڶ�������Ϊ��һ�����ڱ�ԵEn+1��ǰһ�����ڱ�ԵEn֮��λ�������Ҫʵ�ֶ������Ŵ�ͱ��轫En��En+1��֮��Եʱ��������ڱ����н����õ����Ը��س�ŵ�֮ԭ�����ﵽ�����Ŵ�֮���ܡ�������ͼ����˵�������ԭ����

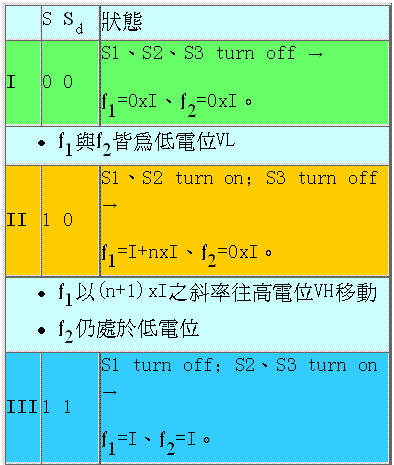

�����Ŵ��·�������������鲻ͬ������֮��ɰ��֣�Charge Pump��CP������ߵ�·��Decision Circuit��DC������ɣ����ֱ��ɴ���Ѷ��SUT��һ�������ӳٺ�֮Ѷ��SUTd������֮��������ơ�����������뷨Ϊ���ò�ͬ���б�ʣ�������ٶȣ�����Ѷ�Ų�ͬ��ʼ�㣨��ת̬��Ե��֮���ԣ����ϳɳ����нϴ�����ʱ����Ե����Ϊ�����������Ŵ�ԭ�������ǽ�SUT��S����SUTd����Sd������λ��ϵ���ֳ��ĸ����䣬Ȼ��ֱ�̽���ڲ�ͬ�����ڵIJ������Ρ����һ��ʾ��

(��һ) ��ɰ��ֲ���״̬��

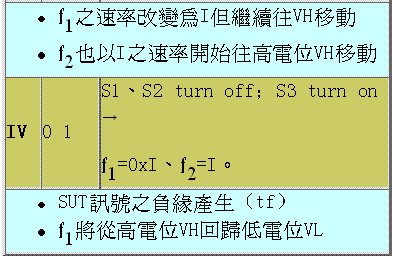

����ͼ�����һ֮���������п��Ե�֪�ڳ�ʼ״̬ʱ��SUT��SUTdΪ�͵�λ�����ؽ�turn off�����Բ����κε����Ը�������������������f1��f2����Ϊ�͵�λ��VL��������������phase���ж�������ʱ��SUT��Ϊ�ߵ�λ��SUTdΪ�͵�λ����ʱf1���ԣ�n+1�����ĵ����Ը��س��pull up����f2��S3 turn off���Խ�����ǰһ״̬�ĵ͵�λ�����ž���Δτ��ʱ���SUTdҲpull high����ʹS3 turn on��S1 turn off����ʱf1��f2��һ����I���ٶ����ߵ�λ�ƶ���������ϸ�۲�Region II��Region III֮���̣�����Δτ�����ʱ����f1���ԽϿ���ٶ���������Region III����ͬ����б�������£���������ΪI������ȵ�����̬λ���������پ���n*Δτʱ���f2��Ҳ�ᵽ���λ����ʱ��ͼ���п��Կ���f1��f2�����趨���ٽ��ѹ��Vth�����������㣬����������ߵ�·��ת̬���жϳ������ɲ������鲻ͬ��λ������Ѷ�ţ�Out1��Out2����������������֮���������ǿ��Լ��Թ�ʽһ����ʾ������������Ĺ�ϵ��

����ʽһ��

����fOUTΪOut1��Out2�����λ��Ŵ��֮���ڶ����ڶ���������fINΪSUT��SUTd�����λ��Ŵ�ǰ֮���ڶ����ڶ�����������A�������Ŵ��ʡ�

��������������������ɽ�ʱ��Ѷ��֮���ڶ����ڶ��������ԷŴ����ֲ�ʱ��-��λת����·�IJ��㡣Ȼ�������⿿���������������Ϊģʽ����ɷŴ�Ŀ�ģ������ٵ�·����ƿ���������²���������������Ŵ��ʵķ����Ի��Dz���Ƶ�ʱ仯�ȣ����������ǻ������ЩЧӦ������֮����

�����Ŵ��·��Pulse Remover��Ƶķ���

(����) ���ű�ʾ

�ڶ����Ŵ��·��������У���Ϊ��ʹ�õ����Ը��س�ŵ�֮�������ﵽ�����Ŵ��������Գ�ŵ�λ�Լ�ʱ�������塣�������ʾ��

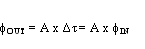

ͼʮ(a)�У�ͨ�������Ŵ��·�ڵ����ʲ���ʱ�����䶶��������ڰ������ʱ����ռ�ı�����С����˵�ɰ��������f1��f2���������̬��ʱ�䣨ts1��ts2��ͨ����С�ڸ�Եת̬��ʱ��tf��

��ͼʮ �����Ŵ��·ʱ��ͼ��(a)Case 1 : tf>ts2��(b)Case 2 : tf≈ts2��(c)Case 3 : tf

�����ڴ�Ƶ�β��������㹻����̬���䣨stable region�����侭���ߵ�·�����֮�����λ��fOUT�����������λ��fIN������ά�ֶ�ֵ��Ҳ�ʹ����Ŵ���AΪconstant������������ʱ��Ƶ����������ͼʮ(b)��ʾ������Ѷ����������tf֮��������ǰ����tf�dz��ӽ�������ts2ʱ�������Ŵ��·��Ȼ����ǿά��ס�Ŵ��ʣ����Դ�ʱ����Ϊ�����ٽ�ֵ����������������ʹ�õ�Ӧ����tf�����ϴ�ı�����Dz���Ƶ�ʼ���������������ts2��tf����������Ŵ��ʽ���ʼ���������Եı仯��

��ͼʮ(c)�ɹ۲���������IJ���ģʽ��f1��f2���Ի�ص���̬λVH��VL��������ת̬��Եtf����δ�ȶ�ǰ�ͳ��֣���f1��f2֮��ѹ�ᱻǿ��ά�����µ�λ�ϣ�Ҳ����VH’��=VH-ΔV����VL’��= VL +ΔV���������������ڵ�һ�����ڣ�initial stage��֮�Ŵ���û�����Ӱ�죬���Ǵ�ͼ�е�֪������һ�����ڣ�next stage������Ϊf1��f2��ѹ��ʼλ�����˱仯�����Ծ��������ٽ��ѹVth�Ľ����Ȼ��֮�ı䡣���仰˵����voltage domain variation��ת����time domain֮phase error����ʱ������ɷŴ��ʱ䶯��������ڶ����ڶ����Ŵ��·�������wide range֮Ӧ��ʱ���ͱ�������һЩ���ƿ�����̬ʱ���ts�ȸ�Եת̬�� tf�緢������˲Ų�����ɷŴ��ʵ�ʧ�档�м��ڴˣ����Ľ����һ��ʹ���������ɹ���֮��ߢȡ���ⷽʽ������֮��

��������֮��ߢȡ���ⷽʽ

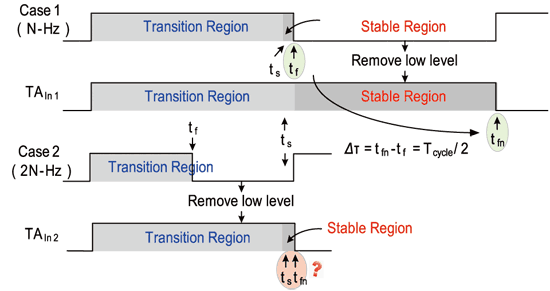

��ͼʮһ �������ɸ���ͼ��

���������ۿ�֪����Ҫʵ��tsf��������ǽ���̬ʱ�����ǰ����������ӳٸ�Եת̬�����֮ʱ�䡣�Ե�·ʵ�ֽǶȶ��ԣ���ts�ǵ����Ը��س����������ĵ�ѹ��ߵ�λVH֮���������Ե���Խ�ص���̬������Խǿ����������ʱ���Խ�硣�������Ŵ�IJ������ǽ��ɲ�ͬ���ʵ���֮�����ã����Ȼ�Ŵ���Ҳ���ܵ�Ӱ�졣����Ϊ�˼�˷Ŵ������������trade-off�����Ľ������ӳ�tf֮������ά�ֲ�ͬ����Ƶ���µĶ����Ŵ��ʡ�

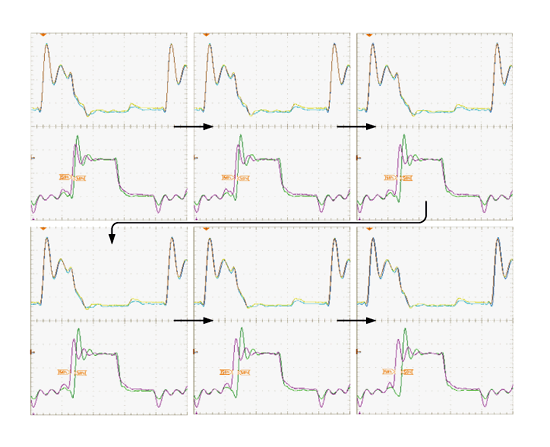

��ͼʮһcase1��ʾΪһ��Ƶ����ʱ��ʾ��ͼ��Ϊ���ö����Ŵ��·�ķŴ���ά�ֶ�ֵ������Ѷ�ŵ�ts����С��tf����worst case�ᷢ����ts����tf��ʱ��㣬��ʱ��̬���伸����������㣬Ҳ����˵�Ŵ��ʻ�dz����ȶ���

Ϊ�˸���������⣬����ǰ��˵���ͱ��轫tfʱ������ӳ١����������ǰѲ����ٶȷ����������������ɵ�·�Ƴ���0.5�����ڣ�����ȡ��̬����֮���ȡ���ͼ��ʾ������case1��Ѷ�����������ΪTAIn1���为Եת̬ʱ��㷢����ʱ�������ӳ���Δτ��=tfn-tf=Tcycle/2�������������̬������֮�Ŵ�2����������Ѵ���Ѷ�ŵ�Ƶ�����Ӻ���������㹻����̬ʱ�䣬���ԷŴ��ʽ����ܵ�clock variation��Ƶ�ʱ䶯֮Ӱ�졣

����ͼʮһ Case2�У�����ʱ��Ѷ�Ų����ٶȳ���������ԼΪCase1�������������Ժ����Թ۲쵽���������������ɻ��ƣ�ts��ԶԶ��Խ��tf����ʱ�����Ŵ��·֮�Ŵ�����Ϊ�����Բ��������������������ɵĻ��ƺ������Ѷ���ٶ�̫�죬����ͬ��ŵ�����������£�tsҲ�dz�����tfn���Ŵ��ʱ��������Ǵ��ڡ������ɴ˿�֪����Ҫ�ﵽwide range�IJ������������κ�Ƶ���£�����Ҫӵ����ͬ����̬���䣬�Ż������õ�constant֮�Ŵ��ʡ��м��ڴˣ����ǽ��������ɵĻ��������ģ�������ά�̶ֹ��Ƴ�0.5�����ڣ��������Ŵ������Ƶ��ÿ����һ������֮�仯����remove number���ɹ�ʽ����ʾ֮��

����ʽ����

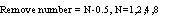

����NΪƵ�ʱ仯�ʡ��ڱ������������������ΪҪ�ﵽ��ʮMHz~1.6GHz֮���������Խ�100MHz��Ϊ����Ƶ��ÿ����һ���ͱ���ı�remove number��ά�ַŴ��ʡ���ͼʮ����ʾ��

��ͼʮ�� �ڸ�����Ƶ�μ�֮�������ɸ���ͼ��

�Ե�·�ĽǶȶ��ԣ�Ҫʵ��ͼʮ���������ɵ�·��ʵ���ѣ�ֻҪ������Ѷ����Ƶ�ξ������Ӧ�ij�Ƶ������ʵ�֡���ʵ������ֱ�ӰѴ���Ѷ�ž�����Ƶ�����ﵽ�������ɣ����ο�����[9]֮˵������Ѷ�ŵĶ���Ҳͬʱ��ᱻ�Ŵ�ԼΪ √n�������⣬��16�ĵ�·������Ҫ4��DFF��ʵ�֣���������Ѷ�ŵ��ﶶ���Ŵ��·ǰ�ͱ��辭������transistor�������ܵ�power noise����thermal noise���ŵ��¶����������⽫������Ӱ������ȷ�ȡ�

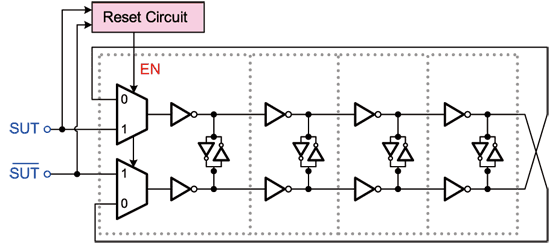

�Ա�Ե���ﵽ��������Ч��

��ͼʮ�� (a)�����֮�����Ŵ��·��(b)��Ե����·����ʾ��ͼ��

��˱��Ľ����ñ�Ե��⣨edge detection��֮�������ﵽ�������ɵ�Ч������ͼʮ��(a)��ʾ������Ҫ�������飺��Ե��������������ɵ�·�����ȣ�������Ѷ��������Ϊ��ά�ַŴ��ʣ����Ƚ���pulse remove�Ķ�������ͼʮ��(b)Ϊ����SUTΪ����Ѷ�ţ�ENΪ�������ɵ�·��������EΪ����������Ĵ���Ѷ�š������������ɵ�·����MUX��ʵ�֣���ɽ��ɿ���s��λ��ѡ��ENѶ��ΪSUT֮/2��/4��/8��/16�Ľ����

����EN������Ե�������data input�ˣ���SUT�����clock input�ˡ���ENΪ�ߵ�λʱ��SUT ��Ե�������ȡ����Hi�����Ѷ��E����pull Hi������ʱ����ѡ��removeΪ/8ʱ����ͼʮ��Case3��ʾ��ENѶ�Ż�ά��4*TSUT��ʱ���תΪ�͵�λ����˵�SUT��һ����Ե���������ȡ����Low����ʹѶ��E pull down��

��ͼ�п��Կ�����Ѷ��SUT��ת����ɹ�remove��3.5��=4-0.5����cycles����SUTѶ��ֻ����һ��ED�����һ����������stable region��ά�ַŴ��ʣ���Ҳ������Ϊ�ô���Ѷ��·��̫�����ı�ԭ��֮�����������������������������Ŵ��������������ɹ���֮��ߢȡ���ⷨ���������κ�Ƶ�������ԷŴ����ʱ���������������ʱ��-��λת����·֮����������������������Ƴ����������ȷ�Ȳ�������⡣

ʱ��-��λת����·��Time-to-Digital Converter��TDC��

��ͼʮ�� �����֮ʱ��-��λת����·��

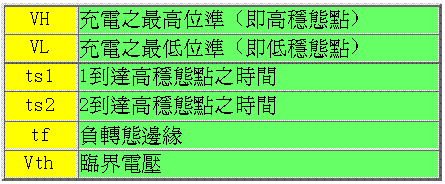

�ڱ�������������µ�ʱ��-��λת����·��������Ϊ��ͳʱ��-��λת����·�����Ͻ���ʹ�ö༶�����������ӳٵ�Ԫ����������λѶ�ţ�Ȼ�����ȡ�����õ���λ�롣Ȼ����Ŀǰ0.13-um���Ƴ���˵�������ܲ�������С�����ӳ�ԼΪ25-ps���ң��༴������ϵͳ���������ܲ��Ե���߽�����Ҳ����25-ps���˹�����ֽ����Ӧ�������������������

�м��ڴˣ����ǽ����öʽ����������λ�ڲ巨����ʵ��һ�ϸ߽�����֮ʱ��-��λת����·����ͼʮ����ʾ������Ҫ������һ��ʽ������Muxed oscillator������λ�ڲ��·��Phase Interpolator��PI���Լ�ȡ�������·�����жʽ������������������λ֮�ο�Ѷ�š���ϴ�ͳʹ��open loop delay chain��close loop���л��ڻ��ƣ����Ի���н�ȷ�ĵ�λ�ӳ�ʱ�䣬�ҽϲ����ܵ��Ƴ�Ư��֮Ӱ�졣������Ϊ��ʹ����ԭ����������λ�����Կɽ��ɲ�����Ƶ�������λ�ӳ�ʱ�䣬�������ٴ���ʹ���ڲ��·���������ɴ���������Խ����ȡ�

��ͼʮ�� �ʽ����֮��·�ܹ�ͼ��

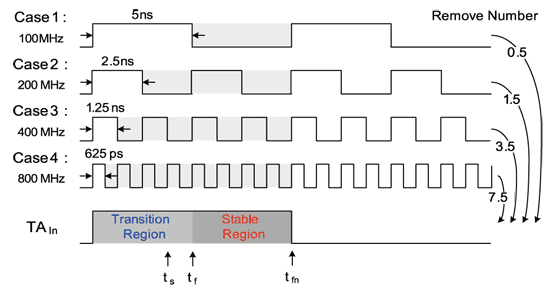

�ʽ������ʱ��-��λת����·����Ϊ��Ҫ�ĵ�·����Ϊ�����������Ѷ�ŵ�����Ե������������ȡ��֮����λ����Ѷ�š���ͼʮ����ʾ��������������ļ��ӳٵ�Ԫ�Լ����õ�·����ɡ����Ϊ�ʽ��������Ϊ�˵�·�������ֲ���ģʽ���ֱ�Ϊ��ģʽ��oscillating mode��������ģʽ��latching mode����ģʽ֮�л��������õ�·��������

��ز���ԭ�����¡�������Ѷ����Ե����ʱ�����õ�·�����ENΪ�͵�·����ʱ���ѡ��0����ͼʮ����ʾ����ʱ��·����Ϊһ������������ȶ��ṩ����λ֮���ٲο�Ѷ�š�Ȼ��ͨ���ڸ�ϵͳ�ж������Բ��ᳬԽ������ڣ�Ҳ���ǣ�1/2��xUI��������ʵÿ�������ڵĶ������ԽԻ��ڰ�������ڽ��������ֻ���ڴ����·�İ���������������ȡ��Ѷ�š����仰˵����ֻ���öʽ��������������ںɹرա�

��˵�����Ѷ�Ÿ���Եһ���������õ�·��ǿ��ENΪ�ߵ�λ����ʱ�������1��·�������Ҳ�����л�������ģʽ����ͼ�пɿ�������ʱ������·�ѱ��жϣ����뼴Ϊ����Ѷ�ţ����ӳٵ�Ԫ��������Ǵ���Ѷ�ŵ��ӳ١����Ǵ���Ѷ�ŵķ����ӳ٣�ֱ������Ե�ֲ����Ż�ָ���ģʽ��������֮���ԡ�

��ͳʱ��-��λת����·����ϣ�ͨ�����ܵ��Ƴ����ܲ�������Сբ�ӳ�������Ϊ�˿˷������⣬���Dz����˳�������λ�ڲ��·��������С��һ���ӳٵ�Ԫ���ṩ���ӳ�ʱ�䡣��λ�ڲ��·��ֱ���뷨��ϣ���ܹ�������������λ���ź�֮�����һ���µ��źţ�������λ���������������λ�źż䣬�����ﵽ�ṩ������λ�����ȵ��ź� [10]��

��

�������ǽ����ڽ����������뷨��ܹ�����Ҫ������ɷŴ����붶�����������ͳ���Է������ԵͶ����������⣬�������϶ʽ��֮ʱ��-��λת����·������������ϵͳ�����ȡ�����Ҳ����·�����������һ�������ɵ�·��ʹ�ô˲���ϵͳ�����ڸ�Ƶ�ν������Ҳ��ԣ�������������ٶȶ�Ӱ�����Ʒ�ʡ�������һ�½��У����ǽ�����HSpice����֤�����֮������ܹ���

ģ����

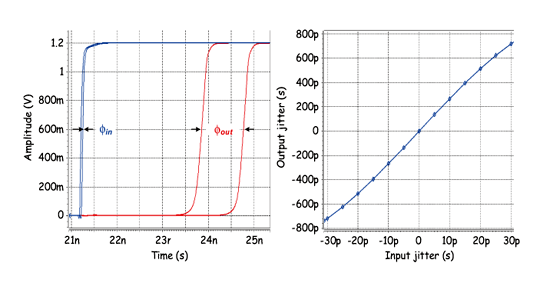

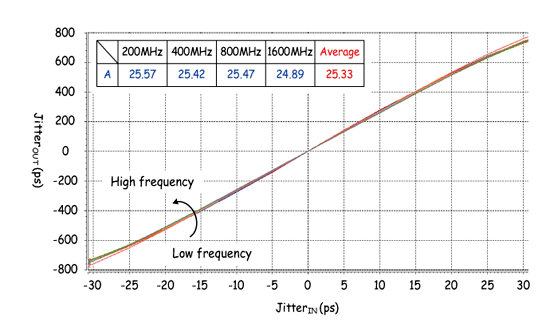

��ͼʮ�� ���Ŵ��·֮ת������ͼ��

��X����붶������Y������������

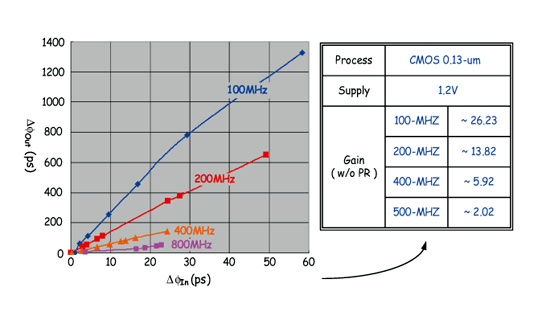

�ڽ��������Լܹ�������Ҫ��Ԫ��Ϊ�����Ŵ��·����Ϊ��Ŵ��ʽ�Ӱ��ϵͳ�������Լ��ȶ��ȣ�������Ҫ��������ȷ�������Ŵ��·�������ԡ���ͼʮ����Ϊ�����Ŵ��·֮ģ��������ʱ����������ʱ�����ɴ˵�·�ɰ�ʱ����Ե������Ҳ����������λ��������������ǿ����ò�ͬ���붶�������۲ⶶ���Ŵ��·֮�������Զȣ���ͼʮ����ʾ������ģ�������ת�����߳�����ͬб�ʣ������˵�·�ķŴ���Ϊһ��ֵ���������߳��ֳ�����б�ʣ�������Թ۲���Ŵ����ڲ�ͬ���붶��ʱ���в�ͬ�ķŴ��ʣ��������DZ�������Ƴ�Ư�ƶԵ�·Ӱ����ģ�������

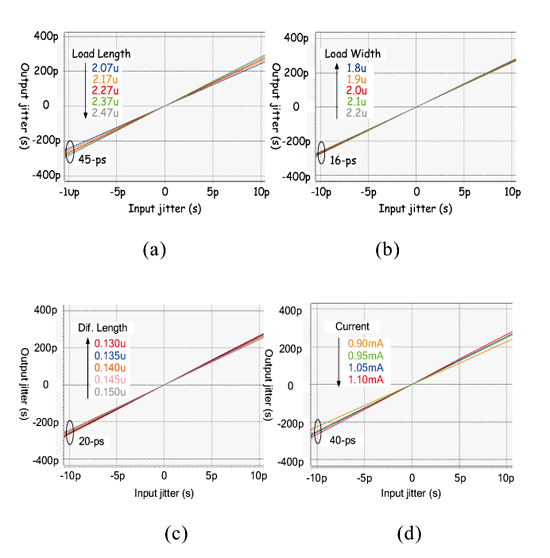

��ͼʮ�� �Ŵ���vs.�Ƴ�Ư�ƣ���a��Load length����b��Load width����c��Diff. pair length����d��Bias current��

��ͼʮ�� �Ŵ��� vs. ����Ƶ�ʡ�

�����Ŵ��·�������

��ǰ���ܹ������Ŵ��·�ǽ��ɵ�����ŵ��ٶ����ﵽ�����Ŵ���˸����Լ������������������Ŵ�ij̶ȣ��������¾�����ĸ��ؼ�������������ģ����ת������ͼ����ͼʮ����ʾ����a������d���ֱ�Ϊ���ص羧��֮length�����ص羧��֮width����Ե羧��֮length��ƫѹ��������ʱ֮ģ�⡣���п��Թ۲���Ŵ�����ά���ڹ̶��ı��ʣ����ڸ��ص��ݣ�length������������仯ʱ����ϵͳ�нϴ��ƫ������Լ40-ps��

����������ϵͳ��������Ϊ���õ��ǷŴ��������ԣ��ٽ�������Ա��ʵõ�ԭʼ��������������Ȼģ�⿴���Ŵ��Ķ���Լ��40-ps�ı��죬�����ԷŴ���25�Ժ������ԼΪ1.6-ps��������������������ֵ�����ɺ��Բ��ơ����⣬ͼʮ��Ϊ�����Ŵ��·�����ڲ�ͬƵ�ε�ת������ͼ�����п����Է��֣��������ڵ�Ƶ���Ǹ�Ƶ����ʱ����Ծ��н��Ƶ�transfer curve�����Լ���֤�˶����Ŵ��·���п�������Χ�Լ����Զ������Ŵ�֮���ԡ����������ģ���֪�����������֮�����Ŵ�ܹ����������ڶ�������ϵͳ�С�

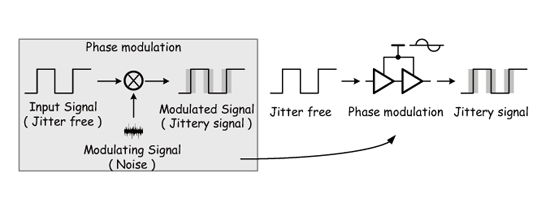

��ͼʮ�� ģ����֤��֮��������ʾ��ͼ��

���ڶ����ڶ���ϵͳ�۲�

Ϊ��ȷ������ϵͳ������ȷ�ԣ��������ǽ�ʵ���������ڶ����ڶ�����ϵͳ�У���˹۲���������ԡ������ڶ����ڶ����IJ�����ʽ�����ǽ�����Ѷ�ŵ��䷨��ʵ�֣���ͼʮ����ʾ�������һ���ɾ��IJο�ʱ����input signal����һ����Ϊ����Դ�ĵ���Ѷ�ţ�modulating signal������λ�����·��phase modulator����������Ѷȥ�ı�����ʱ��ת̬��ʵ�ֶ���������

���Ե�·����������ʵ��λ�����·���ǿɵ�����Դ��ѹ�Ķ༶����������һ����ʱ�����뻺���������ӳٲ��������ӳ����͵�Դ��ѹ�м�������ԡ���ѹԽ���ӳ�ԽС����֮��ѹԽС�ӳپͻ�Խ�����ô˹�ϵ������ֻҪ��������Ϊ��������ѹ���Ϳ��Եõ����Ŷ����仯��ʱ����λ��

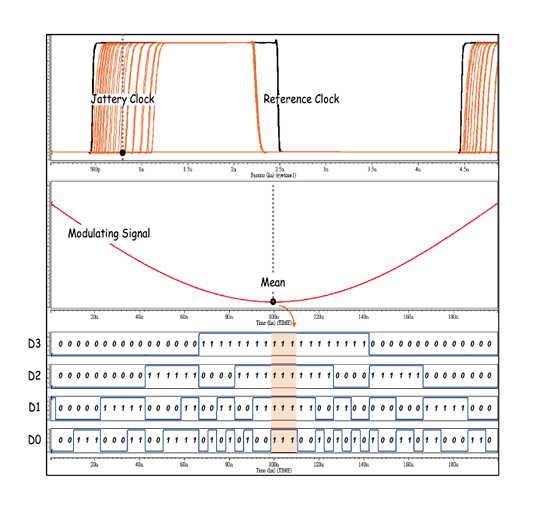

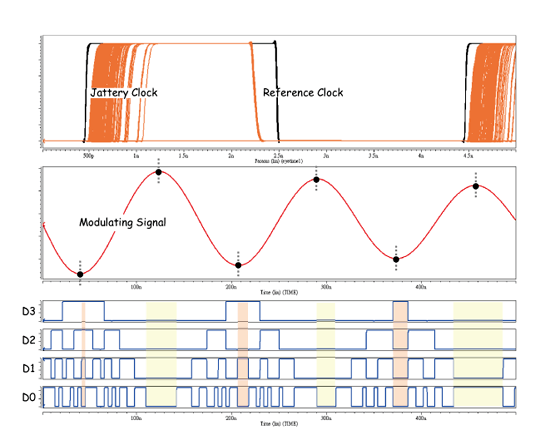

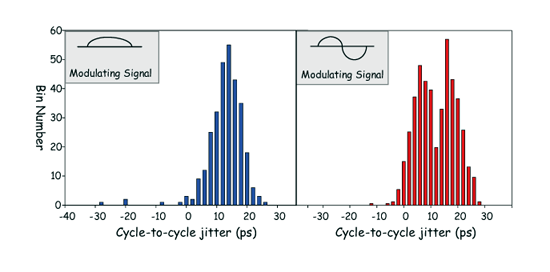

������λ���۲�

Ϊ����֤��ϵͳ�Ƿ�����ȷ�ذ����붶����λ�����������Ҳ���������ֲ�ͬ��̬֮��������֤��һΪ���Ҷ�������һΪ������䶶������ͼ��ʮ�Ͷ�ʮһ��ʾ�Ķ�������λ��֮ģ���������п��Ե�֪�����ϵͳ�ɳɹ������붶����̬�������Ӧ��λ�룬����ֻ�轫��λ����ն����������ɵ�֪���붶������

��ͼ��ʮ ���Ҷ�������������ϵͳ֮��������

��ͼ��ʮһ ������������������ϵͳ֮��������

��������ȷ�ȺͲ���ʱ��������У����㹻���������²���ȷ��������ֵ�߱����������ڲ���ʱ�ͱ�����ϵͳ����ʱ���ۼơ����ǽ�����ǰ��������̬֮�����ֲ�����ʱϵͳ���ͳ����������ֵ����Ϊ�˵�֪����ʵ�����ֲ����������������ۼ����ж������ֲ�����������Խ����ͼ��ʮ����ʾ��

������ֵ��Ӧ����

������ʱ��������ڰ��������Ҷ������ݣ�ͼ��ʮ�������Կɿ�����Ϊһ��˹�ֲ�������һ����ֵ����ֵ���������Ҷ��������ֵ�ϡ�����ͼ������䶶��֮���Խ��������ʾ˫��֮�����ֲ�������˫��ķֲ���Ҳ������ͬ��������Ϊ�������Ѷ��ÿ����ֵ��ѹ��ͬ������ͬ�ķ�ֵ���Ӧ����ͬ����λ�룬�����ڳ�ʱ�䶶�������²Ż���ִ˷ֲ����Ρ�

�������ϵ�˵���ɵ�֪�����������֮������ϵͳ�������Գɹ����������������ɽ��ɳ�ʱ��ķ������ɽ�һ���ص�֪�����ֲ���̬�����ɴ��������������ֵ������������ֲ��n��sigma�Ķ����ֲ���…�ȵȡ�

��ͼ��ʮ�� ��ʱ���ۼƶ�����������

��������Է�֮���Խ��

��ͼ��ʮ�� ��������ʾ��ͼ��ʵ�ʲ���ͼ��

���ÿ�Ƶ��������Ѷ��

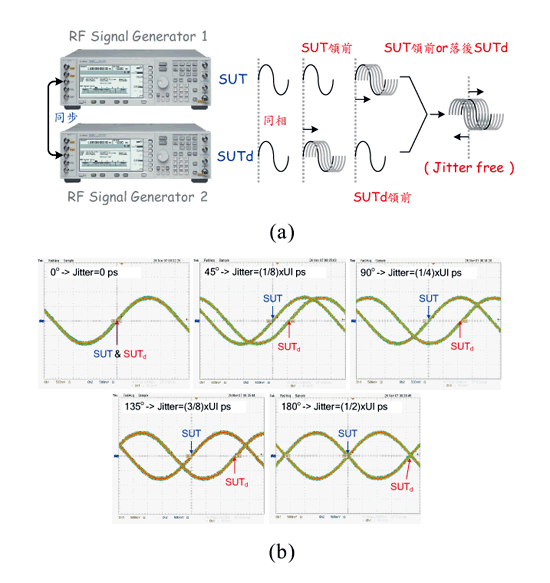

��������Ľ����ϣ����ǿɷ�Ϊ�������ݣ�һΪ��Զ����Ŵ��·�����ԣ���һ��Ϊȫϵͳ���ԡ�����ǰ�ܹ�˵�����ᵽ������������IJ��Լܹ�����Դ���Ѷ��֮���ڶ����ڶ��������ԣ������Ҫһ�ӳٵ�·����ÿ������Ѷ�����ӳ�һ������ʱ��֮Ѷ����ȡ��������Ϊ��Ҫ��֤�����Ŵ��·�������ԣ�����Ҳ��Ҫһ�dz���Ƶ�����Χ��������Ѷ�ţ���˲���ͼ��ʮ���IJ��Է���

�༴����������̨��ƵѶ�Ų��������ֱ��������SUT��SUTd֮����ʱ��Ѷ�ţ���Ϊʱ����ǿ��ͬ�������������ı��κβ���ʱ��SUT��SUTd֮Ѷ�Ž�����ͬ��λ����Ϊ�˲��Զ����Ŵ��·�ķŴ����ԣ��ɽ��ɵ�������һ̨Ѷ�Ų�����֮�ӳ�����������ʵ��ʱ���������Ρ�

��ͼ�п��Թ۲����������Ѷ�Ų�����2���ӳ�������ʵ�����������������Ѷ�Ų�����1���ӳ��������ʵ����ǰ������������˵������ɴﵽ��������Χ֮���ԡ�������Ѷ�Ų������ɲ�����ΧƵ�ʵ���������Ҳ�ɽ�һ�����Զ����Ŵ������Զȡ�

��ͼ��ʮ�� �����Ŵ��·�����ʾ��ͼ��

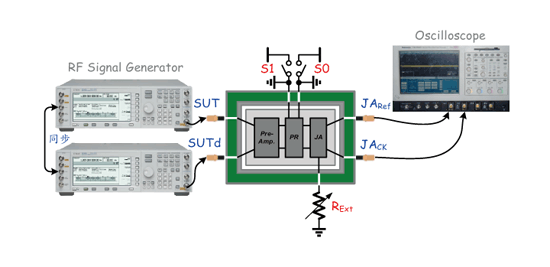

�������Թ���

ͼ��ʮ��Ϊ�����Ŵ��·���Ի���ʾ��ͼ��������Ѷ��Ϊǰ����̨Ѷ�Ų��������ṩ֮Ѷ�š��ھ�Ƭ��ǰ�˻�����Ԥ�ȷŴ�����pre-amplifier��������ת��Ϊ��������֮�����������ɵ�·�붶���Ŵ��·�С�������������·�Ŵ����������ʾ�������۲����Ѷ�ż����λ��ٽ������λ�JACK-JARef������������λ�SUT-SUTd�������ɵõ������Ŵ��·֮�Ŵ��ʡ�

�������Ѷ��Ƶ�ʸı�ʱ���ɽ��ɵ���S1��S0��ѡ���Ϊ�ʵ��������������������������Ŵ��·������ʱ����Ư�ƣ���ɽ��ɵ����ⲿ����RExt�����ı����������ȷ�������Ŵ�����ȷ�ԡ��������������֮���������ɲ��Գ������Ŵ���֮���Զȣ�JitterIn vs. JitterOut��������Ƶ����Ƶ�� vs. �Ŵ��ʣ���Ŵ��ʺ�������������Ĺ�ϵ��

��ͼ��ʮ�� ��������ϵͳ֮�����ʾ��ͼ��

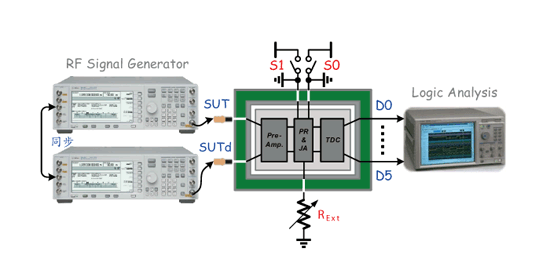

�����������������

����ͼ��ʮ��Ϊ����������ϵͳ֮�����ʾ��ͼ����ǰ�˺�ͼ��ʮ������һ�£������Ŵ��·�����ʱ��-��λת����·������ѽ�������������λ�룬�������ǽ����������ǣ�Logic Analysis��LA�������㼴ʱ���֮��λ�룻��һ����Чʱ��������ٰ��������������֮��������붶������Ƚϣ����ɵ�֪�����֮ϵͳȷ�ȡ�

��ͼ��ʮ�� ���붶�����������֮����ͼ�����ż�ͷ����������붶��������

���ȣ����ǽ�������Ķ����Ŵ��·��ʹ������ڲ�ͬ���붶�����£��۲�Ŵ��ʼ�ı仯����ͼ��ʮ����ʾ��Ϊ�˲��Լ�¼���㣬���Dz���6������pattern����֤��Ҳ����˵����6����ͬ�����붶�������붶���Ŵ��·�У�Ȼ������������������Ի�������Ŵ�����ͼ������Ϊ����֤������������������ɹ���������Ŵ����Զȣ�����Ҳ����ĸ�Ƶ������֤��

��ͼ��ʮ�� �����Ŵ���vs.����Ƶ�ʡ�

�����Ŵ��·���Խ��

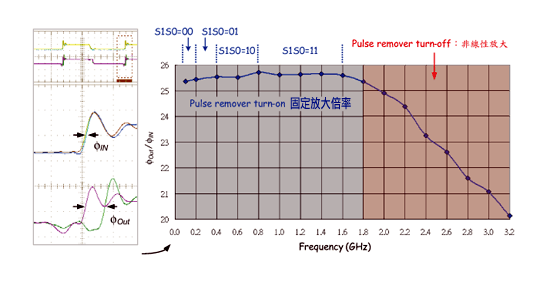

ͼ��ʮ��Ϊ�����Ŵ��·���Խ������ͼ�пɹ۲�����ڵ�Ƶ����ʱ����Ϊ��̬�����㹻��������������������붶���ȣ��뵱������Ƶ���Զ�������Ŵ���Ѷ��Ƶ����������̬������С���ڲ���������������Ŀ�������£��Ŵ��ʻ���֮��С�������Ŵ�����ʧ������ϵͳ����������800-MHz������Ϊ���������ηŴ������½���Լ2�����ң���ʱ����ȫ���ֲ�ʱ��-��λת����·�����Ȳ����ȱ�㡣��˴Ӵ˲��Կɹ۲�������ڸ�Ƶ���ڷŴ��ʽԿ�ά�ַŴ̶�����ֻҪ����Ѷ��Ƶ��һ�仯���ͻ���ɷŴ���ʧ�������ڻ������е����Ρ���˽���������ǰ����˵���ʵ��л����������������ﵽ��Ƶ֮�Ŵ��ʡ�

��ͼ��ʮ����ʾ���ڲ�ͬƵ�β���������ȥ�ı��������ɵ���Ŀ��Ҳ�����л�S0��S1���ö����Ŵ��·�ڲ�ͬƵ���½Ծ����㹻������̬���䡣����Ҳ���ɵ���������轫������·֮�Ŵ�����Щ��������ͼ����ʾ����������������������ʮMHz��1.6GHz������Ŵ���ά����25.5�����ҡ���������1.6GHz����Ϊtfnʱ�����������ts�����̬��λ�ı仯�����ԷŴ��ʿ�ʼ��Щ���ı䡣����Ƶ�ʼ�����������tfn�����ڻ��dz�ǰts����ɷŴ��ʼ����½�������˵�˶����Ŵ��·�����ԷŴ���Ϊ��ʮMHz~1.6GHz���ڴ˱���˵����Ϊ��������ɽ��ɸı��������ɵ���Ŀ����ɣ������������ڸ���Ƶ��������ʱ������ֻ�����죨2��ʽ��ʵ�ּ��ɡ�

��ͼ��ʮ�� �Ŵ�����Ƶ�ʼ�֮��ϵͼ��

��ͼ��ʮ�� �ʽ����֮��Ƶ�ʲ���ͼ��

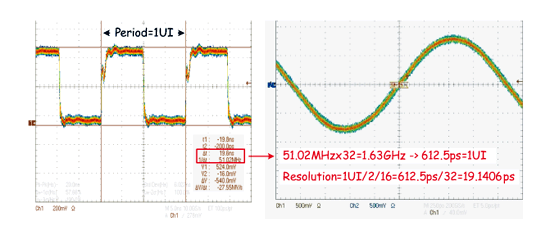

ʱ��-��λ��·��ѽ�����

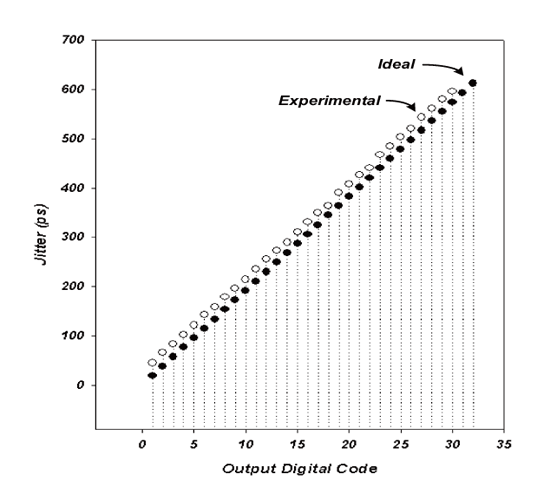

���˶����Ŵ��·�����⣬ʱ��-��λת����·Ҳ��ϵ��ϵͳ��ѽ����ȡ����Ҳ���ɵ������붶�������۲���λ����룬�����Զʽ������Ƶ�������ƽ����ȡ���ͼ��ʮ����ʾ��Ϊ�˲��Է��㣬���ǽ���Ƶ�ʳ���32���۲⣬���Դ�ʱ��-��λת����·����ѽ����ȣ�Ϊ�����ڳ���32����λ�����ڲ�����ã����༴ԼΪ19-ps��

����ͼ��ʮΪ���붶��������λ�����֮����ͼ������ʾ���붶��ÿ����19-ps��λ��Ҳ��֮���ӣ������������������������Լ40-ps�������������������֮����������ϵͳ��������������ֻҪ����������۳����ɣ���Ϊ�������ĵ���ÿ����λ����������Ķ������Ƿ���ͬ��������ǽ�ͼ��ʮ������������л��ַ������������Integral Nonlinearity��INL��֮��������ͼ��ʮһ��ʾ����ʱ��-��λת����·���ƫ����ԼΪ6-ps����0.32LSB��1LSB=19-ps������С��0.5LSB�����Կ�˵����ϵͳ����ʱ������������صĴ���

��ͼ��ʮ ���붶�� vs. ��λ����롷

��ͼ��ʮһ ʱ����λת����֮INL����ͼ��

�ó�ϵͳ������

ȷ���˶����Ŵ��·��ʱ��-��λת����·�������Ժ������ǽ����Ƶ�ϵͳ�����ȡ���Ϊ�Ŵ���A���ӳٵ�Ԫ֮�ӳ�ʱ��ı���Ϊ25.5:19�������ڴ����������ܲ����ѽ����ȼ�Ϊ19-ps/25.5=0.8-ps��ͬ����֤����������Ͻ���������������С�ӳ�ʱ���������Ϊ1:2ʱ���˽��ɰѽ����Ƚ�һ��������0.5-ps���м�����������ģ��֮��������ǿ���˵�˲��Է������ɳɹ�������wide range�Լ�low jitter���ڽ�ʱ���������Լܹ��С�

����

����ǰ���оٵ����ִ�ͳ���Լܹ�������������õ�·��������С�ӳٵ�Ԫ���ӳ�ʱ�䣬�Ե�Ч���Ӳ��Խ����ȡ�Ȼ���������ٶ��������Ƕ���������sub-ps�ȼ������·���Ƴ���֮ƿ��������������ķ�Χ�Ի��ܵ����ơ�

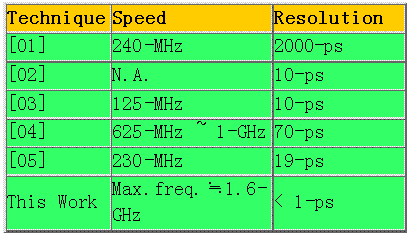

��������֮ԭ���������ͬ�ڴ�ͳ���Լܹ��IJ��Բ��ԡ����Dz��ö����Ŵ�Ĺ������Դ���Ѷ�Ŷ����������ڷŴ�Ȼ������ʱ��-��λת����·�������������ٰѵõ��������λ����ԷŴ��ʣ����ɻ�ԭ��ԭ�������ڶ����ڶ�����������Ϊ���ô˲��Լܹ��ܲ������κ�Ƶ���£���˻����õ�ߢȡ�����������ɵIJ��Է��������������Ŵ�ʱ����̬ʱ�䣬�Եõ��̶��Ŵ��ʣ�����������Ƶ�ʱ仯�����������������Ա����������������ڴ�ͳ���Է�ʽ�����߱���Ƶ�������Ͷ��������ԡ��߽����ȡ��ɱ��͡��ܲ��Ի������Ƴ̶�С���ŵ㡣�����Ƚ��������ʾ��

(����) ���ּܹ��Ƚϱ�

���꣩

��ת�Թ���Ժϵͳ��Ƭ�Ƽ����ļ����ڿ���8�ڡ�������褺�֣�˶G��